# EFFECTE OF THERMAL ANNEALINEG ON THE ELECTRCAL PROPERTIES OF Pbs/si HETEROJUNCTION

## **ZUHAIR H. JAWAD**

Department of science, College of Basic Education , Diyala University Baqubah, Diyala, Iraq

## Abstract

In this research the electrical properties for heterojunction devices have been improved by process of simple annealing temperature about one hour period. The results have been explained that the influential of analysis process on electrical properties during the clearest improve for devices properties at special temperature.

# **1. Introduction**

The process of simple annealing temperature represents is one of the essential and publical ways for solve the special problems that happened during the growths subtraction[1]. The process of annealing temperature has several uses. It is used for improving the value of detectors and transistors which is made from semiconductors thin films integrated circuits[2]. and devices are receiving Heterostructure now considerable interest because of their potentially high performance per unit cost, where low technological complexity and low temperature (as compared with homojunction devices) can be employed. A substantial amount of work has been published on heterojunctions[3-6]. The last decade an increasing competitive witnessed attention on the narrow- bandgap/widebandgap heterojunctions [7-10]. In this combination, efficient IR photodetectors can be obtained when the wide-bandgap semiconductor acts as an window layer and the narrow- bandgap semiconductor acts as an absorber. Foremost in those heterojunction detectors is the PbS/Si heterojunction[12-14]. This hetero-pair was prepared by depositing PbS films onto Si in many routes, such as thermal evaporation[15] or chemical-solution growth[16]. However, the fabrication PbS/Si heterojunction by chemical spray pyrolysis technique is not found . this note prompted us to fabricate PbS/Si heterojunction by utilizing chemical spray pyrolysis technique.

# **2. Experimental Procedure**

# **2.1. Sample preparation**

By chemical spray pyrolysis Leadsupplied has been deposited on to monocrystalline P-type silicon wafer (111) orientation to prepare PbS/Si heterodiode. The deposition procedure was achieved by pyrolytic spray of 0.2 M of aqueous solution of  $Pb(NO_3)_2$  and thiourea on the mirror-like surface of the wafer. The temperature analysis of the films deposited which estimated approximately from the gravimetric method was varied between. The substrate temperature was maintained during spraying at 350°C. This optimum temperature was selected from five different temperatures. Ohmic contacts were made as the following :frontal metal contact was done after PbS deposition by evaporating 250nm pure Al through a special mask, while the deposition of back metal contact was done before PbS deposition.

## 2.2. The process of annealing

The essential way of annealing temperature has been used by oven at temperature between (250-650  $^{\circ}$ C) for one hour.

## **2.3.** Electrical properties

I-V and C-V characteristics were measured after wiring the fabricated diodes. The main parameters were extracted from these measurements viz; ideality factor n and built-in voltage  $V_{bi}$ . Four-point probe method was used to determine the conductivity of PbS deposited films.

#### 3. Results and Discussion

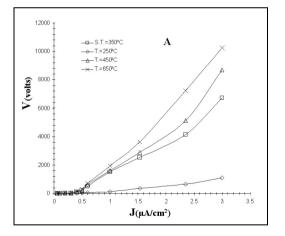

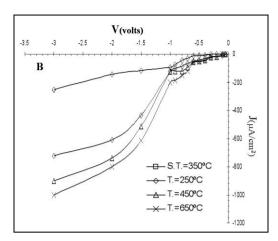

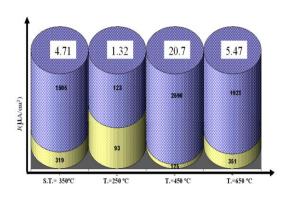

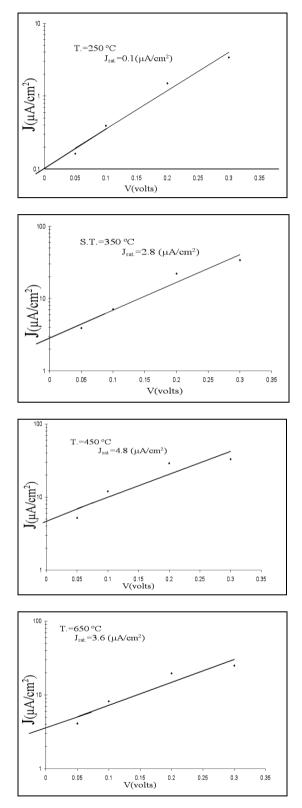

Results of four probe measurements revealed that the conductivity of PbS films is n-type. Thus, it is anticipated that PbS/Si heterojunction will take the form of an iso type heterodiode. Fig.(1) shows J-V curves for the heterodiodes prepared in different annealing temperatures of PbS thin films (as shows in the legend). From this figure, it is shown that the behavior of J-V curves proposed is similar to that bv Anderson[14]. It can be seen that the diodes exhibit good rectification factor with value approaches 20.7 at 1V bias samples for 450 °C annealing temperature as shown in fig. (2). A semi-log J-V plot at the forward bias is demonstrated in Fig. (3) and the reverse saturation current density J<sub>sat</sub> represents the intersection of

Figure 1. J-V Curves, a-Forward, b-Reverse

Figure 2. Forward and Reverse Current As afunction of annealing temperature

Figure 3. Semi-log J-V Characteristics

the straight line with current axis. At large,  $J_{sat}$ . decreases when T.=450 °C .This can be attributed as following; The

junction will be located near to surface which leads to high leakage current (J<sub>sat</sub> is high), The junction will be located far from the surface which leads to decrease in leakage current. At high annealing temperature 650 °C, strains taken place due to lattice mismatch effect would substantial cause amount of dislocations[18] which in turn will produce a great deal of recombination centers, hence recombination current component will be added to the diffusion current component i.e., J<sub>sat</sub> will be increased.

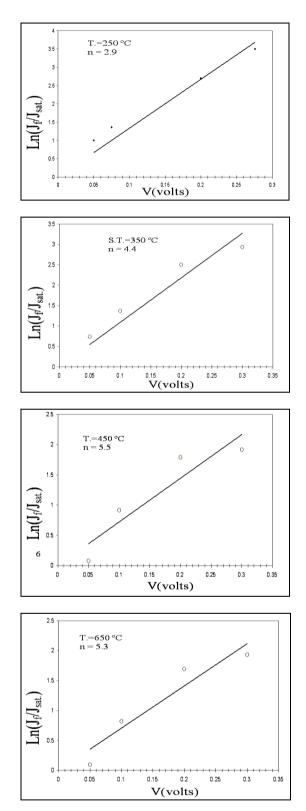

fig.(4) is the  $\ln(J_F/J_{sat}) - V$  plot. The slop of this plot is the direct method to calculate ideality factor n. From this figure, it can be seen that the diodes prepared at 250 °C annealing temperature has a better ideality factor.

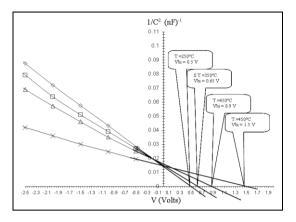

Fig.(5) is the reciprocal of square capacitance against reverse bias voltage will form a straight-line plot. The extrapolated straight-line intercepts the voltage axis at the point of built-in voltage.

#### 4. Conclusions

Extracted from the above mentioned, we can draw the following :low-cost CSP technique is suitable to fabricate PbS/Si heterojunction diodes. This heterojunction will be anisotype when silicon substrate is p-type. annealing temperature of PbS thin films greatly affects the device characteristics. There are specific border for annealing temperature inorder to be positive effect in improving electrical properties orelse it be come negative effect. An essential properties that we have getting during annealing temperature about 450°C has abetter results .

Figure 4.  $ln(J_F/J_{sat})$  against Forward Voltage for Ideality Factor calculations

Figure 5. Reciprocal of Square Capacitance with Bias Voltage

#### **5. References**

1.V.Allmen "Physics process in laser material interaction " Plenum press. p:52 (1983).

2. Makram A. Mutalb , J. of engineering and technology , **27**, No.14, (2009).

3. H. kobayshi , Y . kogetsu , T. ishude ,Y. nakato , " J. Appl. Phys. " **74**, p:4756 (1993).

4. T. ishida , H. kouno , H. kobayshi , y. nakato " J. Electrochemical Soc." **141**, 1357 (1994).

5. T. Tamagawa , T. shintasi , H.ueba , C. Tatsusyama , Thin Solid Films **237** p:282 (1994).

6. D. L. Young , T. J. Coontts , V. I. Kaydanov " Rev. Sei. Instrum " **71**, p:462 (2000).

7. Y. J. Mii ,y. H. xie , E. A. Fizgerald , D. Monroe F. A. Thiel , B. E. Weir , L. C. Feld man , J. Appl. Phys. 59, p:1611 (1991).

8. S.M. Beenjamin , J. Hwang " J. Appl. Phys. " **75**, p:338 (1994).

9. O. Nur, and M. Willander, J. Appl. Phys., 78, p:7063 (1995).

10. J. Kolodzey " Vacuum Solutions " 9, p:5 (1995).

11. A. U. Uble, A. R. Junghare , N. A. Wadibhasme , A. S. Daruapurkar , R. B. Mankar , V.S. Sangawar ,Turk. J. Phys. **31**, pp279-286 (2007).

12. L. Pintilie , E. Pentia , D. Petre , I. Pintilie , T. Botila , Proc. 17th Annual Semiconductor Conf. , pp 207-210 (1994).

13. I. Pintilie , E. Pentia , L. Pintilie . D. Petre , T. Botila , C. Constantin , J. Appl. Phys. **,78**, p:1713(1995).

14. T.Botila , E. Pentia , L. Pintilie , Proc. IEEE , No. 99 P:511(1999).

15. M. Salman " Study of Electrical and Photovoltaic Properties of PbS/Si Heterojunction Detector ", M.S.c Thesis , University of Applied Sciences , (2000).

16. H. Elabd , and A. J. Steckle , J, Appl. Phys. , **51**, p:726 (1980).

17. R. L. Anderson , Solid State Electron. , **5**, p:341 (1962).

18. A.G. Milnes , and D. IL. Fecht "Heterojunctions and Metal-Semiconductor Junctions Academic Press New York and London" pp 226-228 (1972).