## Design of RF Power Amplifiers using Parallel-Series Power Combining Transformers

#### Suhad. H. Jasim

Electrical Engineering Department, University of Technology/Baghdad.

Email: suhadhusin@yahoo.com **Dr.Ahmed S. Ezzulddin**6

Electrical Engineering Department, University of Technology/Baghdad.

Email: ase.uot@gmail.com

Revised on: 2/9/2014 & Accepted on: 8/1/2015

#### **ABSTRACT**

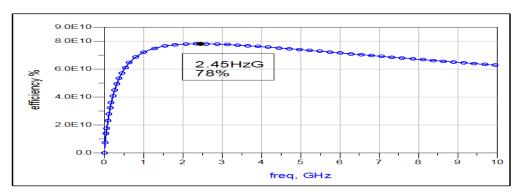

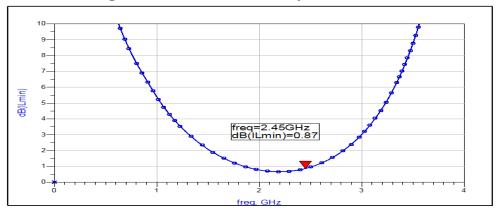

This paper presents the design of a one watt-level RF CMOS Power Amplifier (PA) based on power combining transformers PSCT in 0.13 µm technology using ADS 2011.10. The PA incorporates a parallel combination of four differential PA cores to generate high output power with acceptable efficiency and linearity. The first part the design for class-AB PA for WLAN applications is presented. The PA delivers an Output Power (Pout) of 30 dBm, Power Gain (Gp) of 30 dB and 40% PAE using 2.5 V supply. In the second part a class-E PA is designed to provide an output power of 30 dBm, power gain of 30 dB, and 54% PAE at 2.45 GHz using 1.6 V supply. The layout of the transformers is designed and simulated with momentum RF EM simulator of ADS 2011.10 in order to realize a fully integrated power amplifier. The simulated efficiency of the designed transformer was 78% with minimum insertion losses (*ILmin*) of 0.87 dB.

# تصميم مضخمات قدرة راديوية التردد بتقنية CMOS مع محولات جامعة للقدرة النوع المتوالي PSCT

#### الخلاصة

يتضمن هذا البحث تصميم ومحاكاة لاثنين من مضخمات القدرة راديوية التردد عالية الكفاءة وبمستوى قدرة يصل الى الواط مع محولات جامعة نوع PSCT باستخدام تقنية CMOS وباجراء ( $0.13~\mu m$ ) بمساعدة حقيبة المحاكاة ADS 2011.10 للترانزستر MOSFET. تم في الجزء الأول حقيبة المحاكاة AB ويصلح للاستخدام في تطبيقات WLAN. تمكن هذا المضخم من تجهيز قدرة تصميم مضخم قدرة من الصنف AB ويصلح للاستخدام في تطبيقات WLAN. تمكن هذا المضخم من تجهيز قدرة مثاره المحال 30 dBm في الجزء الثاني فقد تم تصميم مضخم قدرة من الصنف E وربح قدرة مؤدا المضخم من تجهيز قدرة خرج مقدارها 30 dBm وربح قدرة مثارة المحول على الرقاقة قدرة مضافة 0.02 والمستخدم مع المضخمين المقترحين، كذلك تمت المحاكاة باستخدام طريقة الزخم الجامع على الرقاقة نوع PSCT والمستخدم مع المضخمين المقترحين، كذلك تمت المحاكاة باستخدام طريقة الزخم

الكهرومغناطيسي للموجات الرادوية واظهرت النتائج للمحول PSCT كفاءة مقدارها %78 وخسائر ادراج صغرى 0.87 dB.

**Keywords:** RF power amplifier, class-E, class-AB, CMOS technology, power combining transformer.

## INTRODUCTION

MOS has for a long time been a good choice for digital integrated circuits (IC) due to its low cost, high level of integration and constant enhancements in its performance. Due to the significant scaling of MOS transistors, the transition frequency has reached well beyond 100 GHz and CMOS technology have become popular in wireless applications. At high frequencies, the major difficulty for CMOS PA is to achieve high output power. This is because at high frequencies, CMOS has low DC bias voltage of only about 2 volts. This low DC bias voltage has two effects, first relatively low RF output power due to low DC input power for any reasonable value of DC input current, second the optimum impedance is proportional to  $(V_{DC}/I_{DC})$ . Low DC supply voltage leads to low RF impedance, which is very difficult to match to 50 ohms load impedance without losses. Furthermore, silicon substrate is usually conductive, which results in substantial additional loss at RF frequencies.

## **Power Combining Techniques**

Transform-type combiner can be categorized as Series-Combining Transformers (SCTs) and Parallel-Combining Transformers (PCTs) according to their ways of voltage and current combining at the load. The advantage of PCT configuration is a reduction of the secondary inductor losses due to a reduction of the current flowing through them but at the cost of a larger area and a lower self-resonant frequency. Moreover, the PCT requires higher turn ratios in order to get the same output impedance compared to a SCT, which increases the losses in practice. On the other hand, a combination of SCT and PCT topologies is also possible in order to combine the advantages of both transformer topologies in a Parallel-Series Combining Transformer (PSCT) topology [1].

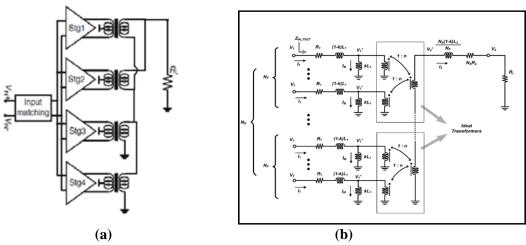

The hybrid-type power combining transformer (PSCT) performs the parallel (or current) and the series (or voltage) combining simultaneously in a single structure enabling the implementation of the power combining transformer in a smaller form-factor compared to the SCT. Moreover, the mutual inductance at the primary side in the PSCT is increased due to additional coupling between adjacent primary inductors, leading to improved efficiency and PTR (Power Transmission Ratio). The PSCT topology and its equivalent circuit model are presented in Figure (1).

The total combining inputs in the PSCT is  $M = N_P * N_S$  where  $N_P$ ,  $N_S$  are the parallel and series combining parts respectively. the input impedance of the PSCT can be obtained by the following equations [1]:

$$Z_{IN-PSCT} = Z_{1-PSCT} + \frac{N_P}{N_S N^2} \left[ \frac{1}{1 + \frac{Z_2 - PSCT}{j\omega K N^2} N_S L_1} \right] Z_{2-PSCT} \qquad ...(1)$$

If the coupling effect and the frequency dependent inductor are ignored, the input impedance of the PSCT can be simplified as:

$$Z_{IN-PSCT-Ideal} = \frac{N_P}{N_S N^2} R_L \qquad ...(2)$$

The input impedance of the PSCT is negligibly affected by the number of combining inputs if the number of series and parallel combining parts are same. The efficiency and the optimal primary inductance value of the PSCT can be obtained by the following equations [1]:

$$L_{1\_OPT\_PSCT} = \frac{R_L}{N_S N^2 \omega} \sqrt{\frac{1}{Q^2} + \frac{1}{N_P^2} + \frac{K^2}{N_P}} \qquad ...(3)$$

$$\eta_{PSCT} = \frac{\omega L_1}{\frac{N_P N_S N^2}{Q K^2 R_L} \left(\frac{1}{Q^2} + \frac{1}{N_P^2} + \frac{K^2}{N_P}\right) (\omega L_1)^2 + \left(\frac{2N_P}{Q^2 K^2} + 1\right) (\omega L_1) + \frac{N_P R_L}{N_S N^2 Q K^2}}$$

...(4)

#### Where

N represents the turn ratio of the transformer, K is the coupling factor, and Q is the quality factor.

Figure (1): (a) Simplified schematic of the PSCT topology, (b) The equivalent circuit model of the transformer.

## Design of a Watt-Level Class AB Power Amplifier for WLAN Applications

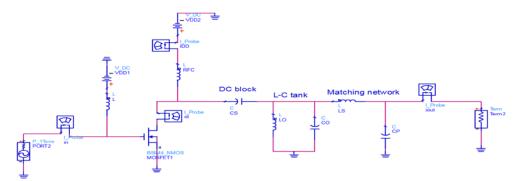

In Class AB, the conduction angle is between  $180^{\circ}$  and  $360^{\circ}$ , the DC bias voltage of the gate-to-source  $(V_{GS})$  is slightly above the threshold voltage  $(V_T)$  and the transistor is biased at a small drain current. As the name suggests, class-AB is the intermediate class between class-A and class-B. A single-ended class-AB power amplifier topology is shown in Figure (2). For a 0.13  $\mu$ m CMOS, 1.2 V and 2.5 V are available. Using

Equation (5) the deliverable output power to 50  $\Omega$  load are 14.4 mW and 62.5 mW under 1.2 V and 2.5 V respectively without any impedance transformation [2]:

$$P_{OUT} = \frac{V_{DD}^2}{2R_I} \qquad \dots (5)$$

$$P_{OUT} = \frac{V_{DD}^2}{2R_L} \qquad ...(5)$$

$$R_{OPT} = \frac{V_{DD}^2}{2P_{MAX}} \qquad ...(6)$$

Equation (6) gives the optimum load to be presented at the PA outout, Under 1.2 V and 2.5 V for an output power 125 mW are 6  $\Omega$  and 25  $\Omega$  respectively. It is clear that 1.2 V is not sufficient because impedance transformation between 6  $\Omega$  and 50  $\Omega$  is too hard to be realized in practice. So, 2.5 V is a good choice for the design. The LC tank circuit  $(L_0, C_0)$  is designed to resonate at  $\omega_0$  and block higher harmonics from proceeding towards the load, so that [3]:

proceeding towards the road, so that [5]:

$$X_{Co} = X_{Lo} = \frac{R_{OPT}}{Q_L} \qquad ...(7)$$

$$L_o = \frac{X_L}{\omega_o} \qquad ...(8)$$

$$C_o = \frac{1}{\omega_o X_C} \qquad ...(9)$$

$$L_o = \frac{x_L}{\omega} \qquad ... (8)$$

$$C_o = \frac{1}{\omega_o X_C} \tag{9}$$

#### Where

$Q_L$  is the load quality factor and is selected to be 15. Using the load pull simulation, the value of the optimum load impedance obtained from the simulation ( $Z_{QPT} = 13.132 +$ j3.026) at which the individual PA can deliver 25.6 dBm with maximum PAE.

Figure (2): Schematic of a single stage class \_AB power amplifier. **Class - AB Power Amplifier Design Based on PSCT**

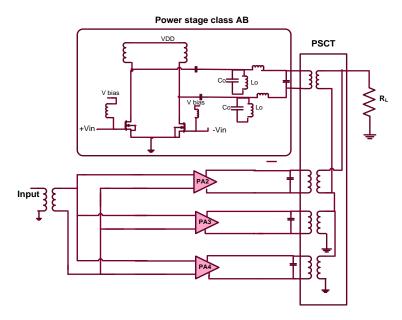

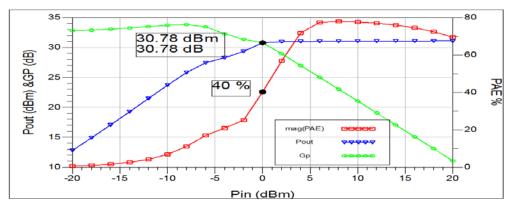

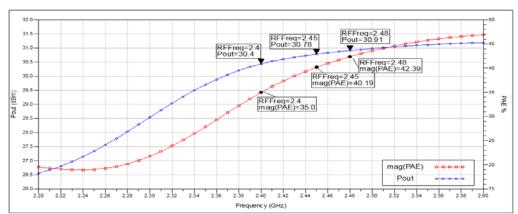

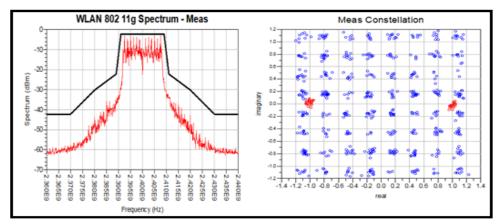

The PA is a four stages, all transformer-coupled design, the turn ratio of the transformer can be determined using Equation (4) with  $N_P$  and  $N_S$  are equal and  $Z_{IN-PSCT-Ideal}$  is the optimum load impedance of the PA that is determined by the load pull simulation  $|Z_{OPT}| = 3.4$ ,  $R_L$  is  $50 \Omega$ . The schematic and the performance of the PA are shown in Figure (3) and (4) respectively. The power amplifier delivers an output power of 30 dBm with PAE of 40% at an input signal level of 0dBm. The simulated performance of the PA as a function of frequency for an input power of 0 dBm is shown in Figure (5). As shown from this figure, the minimum PAE is 40 % while the output power PA remains almost flat over the band which is from 2.4 GHz to 2.48 GHz . Using WLAN IEEE 802.11g transmitter test bench of ADS 2011.10, the measured spectrums and constellations for the WLAN signals are presented in Figure (6). Finally, The characteristics of the PA, compared with other recent works are summarized in Table (1).

Figure (3): Schematic of the PA based on PSCT.

Figure (4): Simulation results of class AB PA based on PSCT.

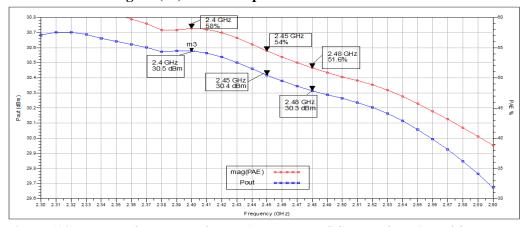

Figure (5): The performance of the PA based as a function of frequency.

Figure (6): Spectrum and constellation for WLAN 54 Mbps 64-QAM signal.

Table (1): Performance comparison of watt-level class AB PAs.

| Reference           | [3]     | [5]    | [6]     | [1]    | [7]  | This<br>Work |

|---------------------|---------|--------|---------|--------|------|--------------|

| Year                | 2009    | 2011   | 2012    | 2012   | 2013 | 2014         |

| CMOS Technology     | 0.13 µm | 0.18µm | 0.90 nm | 0.18µm | 65nm | 0.13         |

| Frequency (GHz)     | 2.4     | 0.9    | 2.3     | 2.4    | 2.4  | 2.45         |

| Pout (dBm)          | 30      | 29     | 30.1    | 23.5   | 33.5 | 30           |

| PAE (%)             | 18      | 24     | 33      | 34.9   | 37.6 | 40           |

| $V_{DD}(V)$         | 1.8     | 3.3    | 1       | 3.2    | 3.3  | 2.5          |

| Combining technique | SCT     | SCT    | PCT     | PSCT   | PCT  | PSCT         |

## Design of a Watt Level Class-E Power Amplifier using Power-Combining **Transformers**

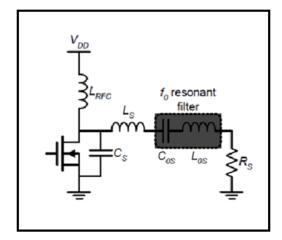

A single-ended class-E amplifier with shunt capacitor topology is shown in Figure (7). The component values of the single ended class E PA are calculated at output power 125 mW (≈ 21 dBm), operating frequency 2.45 GHz. In 0.13 μm CMOS technology drain supply voltage of 1.2 V and 2.5 V are available, both values will provide an impedance transformation ratio that is too hard to be realized in practice for the PA design based on PSCT. Therefore the supply voltage is chosen to be 1.6 V. The components values are determined using the following equations [10]:

$$R_{S} = \frac{8V_{DD}^{2}}{(\pi^{2}+4)P_{OUT}} \qquad ...(10)$$

$$L_{S} = \frac{\pi(\pi^{2}-4)V_{DD}^{2}}{2(\pi^{2}+4)\omega_{o}P_{OUT}} \qquad ...(11)$$

$$C_{S} = \frac{P_{OUT}}{\pi\omega_{o}V_{DD}^{2}} \qquad ...(12)$$

$$C_{OS} = \frac{1}{\omega_{o}Q_{LS}R_{S}} \qquad ...(13)$$

$$L_{OS} = \frac{Q_{LS}R_{S}}{\omega_{o}} \qquad ...(14)$$

$$L_S = \frac{\pi(\pi^2 - 4) V_{DD}^2}{2(\pi^2 + 4) w_0 P_{DMT}} \qquad ...(11)$$

$$C_S = \frac{P_{OUT}}{\pi \omega_0 V_{PP}^2} \qquad \dots (12)$$

$$C_{OS} = \frac{1}{\omega_0 Q_1 s R_S} \tag{13}$$

$$L_{OS} = \frac{Q_{LS}R_S}{\omega_o} \qquad ...(14)$$

$R_{s}$  is usually called optimum load resistance  $(R_{out})$  designed according to the specification on output power and the supply voltage. The series tank, consisting of  $L_{OS}$  and  $C_{OS}$ , is inserted to suppress higher harmonic content in the load.  $L_{RFC}$  can be calculated by the resonant equation of an LC tank [8]:

$$L_{\text{RFC}} = \frac{1}{\omega_o^2 c_1} = \frac{1}{\omega_o^2 (c_p - c_s)}$$

...(15)

where

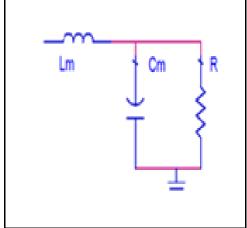

$C_1$  is the cancelation capacitance by the inductor,  $C_p$  is the MOSFET output capacitance and  $C_s$  is the capacitance of the class\_E PA. LC tank is the most simple and straight forward matching network that has been widely used in all kinds of PAs, however. A single-stage LC tank matching network basically has a forms as shown in Figure (8). The values of  $L_m$ ,  $C_m$ , and  $L_{total}$  can be calculated using the following equations [9]:

$$L_{m} = \frac{\sqrt{R_{opt}(R_{L} - R_{opt})}}{\omega_{o}} \qquad ...(16)$$

$$C_{m} = \frac{R_{L}}{\omega_{o}}$$

$$...(17)$$

$$L_{total} = L_{x} + L_{m} \qquad ...(18)$$

Figure (7): Single-ended class-E PA with shunt capacitor.

Figure (8): Single-stage L-C matching network

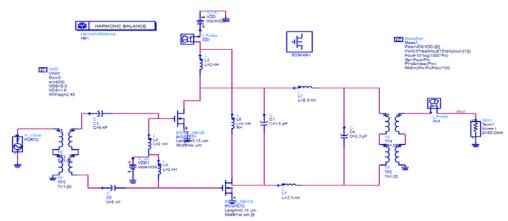

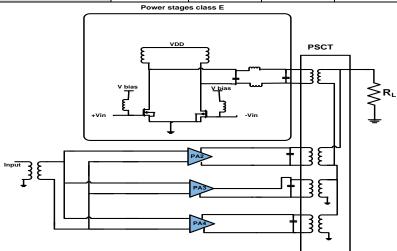

## Class-E Power Amplifier Design Based on PSCT

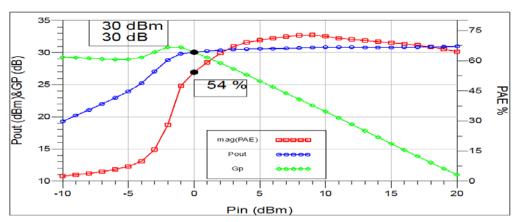

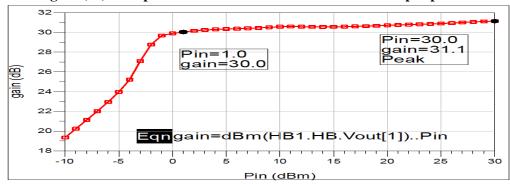

The designed PA incorporates four stages differential stages with each stage delivers 250 mW approximately based on PSCT power combining. The topology of differential PA is shown in Figure(9). The schematic and the performance of the designed PA based on PSCT as a function of the input power are shown in Figure (10) and (11) respectively, it delivers an output power of 30 dBm with PAE of 54% at input power 0 dBm. In order to estimate the linearity of the PA, the 1-dB gain compression simulation is performed, the simulation result is shown in Figure (12). The power amplifier reaches its output 1-dB compression at 30 dBm, with an input power level of 1 dBm. The simulated performance of the PA as a function of frequency for an input power of 0 dBm is shown in Figure (13). As shown from this figure, the output power of the PA remains almost flat over the band, which is from 2.4 GHz to 2.48 GHz. The minimum PAE is 51.6 % . The performance of the designed PA is compared with other state-of-the-art linear CMOS PAs as illustrated in Table (2).

Figure (9): Schematic of differential class-E power amplifier.

Table (2): Performance comparison of watt-level class E PAs.

| Reference                       | [10]    | [11]   | [12]   | [13]    | This<br>Work |

|---------------------------------|---------|--------|--------|---------|--------------|

| Year                            | 2008    | 2009   | 2012   | 2013    | 2014         |

| CMOS Technology                 | 0.18 µm | 0.18µm | 0.18µm | 0.25 µm | 0.13         |

| Frequency (GHz)                 | 1.8     | 1.71   | 5.2    | 5.3     | 2.45         |

| Pout (dBm)                      | 31.2    | 33.4   | 23.4   | 30.3    | 30           |

| PAE (%)                         | 41      | 50     | 21     | 17.8    | 54           |

| $V_{DD}\left( \mathbf{V} ight)$ | 3.3     | 3.3    | 3.3    | 6.35    | 1.6          |

| Combining technique             | PCT     | SCT    | PCT    | PSCT    | PSCT         |

Figure (10): Schematic of the PA based on PSCT.

Figure (11): The performance of the PA as a function of input power.

Figure (12): Gain compression simulation result.

Figure (13): The performance of the PA based on PSCT as a function of frequency.

## **EM-Simulation of the Proposed Transformer**

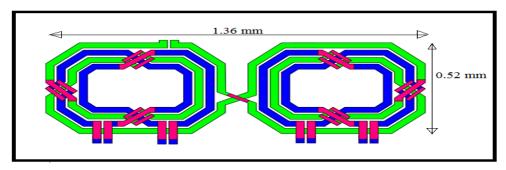

The power combining transformer PSCT is implemented with four primary inductors i.e. four power amplifier stages. The PSCT is composed of a series combining

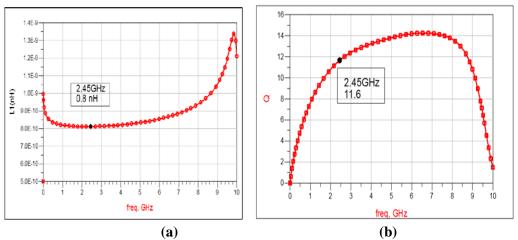

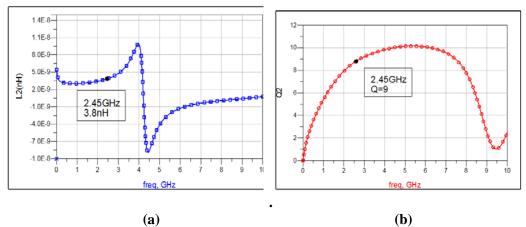

of two PCTs that have two primary inductors interwoven to the secondary inductor. Thus, the transformer exhibits a series-combining of two parallel-combining parts (i.e.,  $N_P = 2$ ,  $N_S = 2$ ) with the total combining inputs of M = 4. The turn ratio of the PCT is  $(N_P \times 1: n)$ is used fixed to ensure that  $(N_S = N_P)$ . The transformer was implemented using two thick metals (4µm-thick aluminum and 3µm-thick copper) that are connected through whole via trace as shown in Figure (14). The width of the inductor metal traces (30 µm) was chosen. The EM simulation shows that each primary inductor and the secondary inductor have the self inductance of 0.8 nH and 3.8 nH with quality factor the of 11.6 and 9 at 2.45 GHz, respectively, the size of the PSCT layout is  $1.36 \times 0.52 \text{ } mm^2$ . The quality factor (Q) can be expressed by the ratio between the imaginary and real part of the input impedance

$$Q_1 = \frac{imag(Z_{11})}{real(Z_{11})} = \frac{imag(^1/Y_{11})}{real(^1/Y_{11})} \qquad ...(19)$$

$$Q_2 = \frac{imag(Z_{22})}{real(Z_{22})} = \frac{imag(^1/_{Y_{22}})}{real(^1/_{Y_{22}})} \qquad ...(20)$$

The inductance can be extracted from the input resistance:

$$L_{1} = \frac{imag(Z_{11})}{\omega} = \frac{imag(^{1}/Y_{11})}{\omega} \qquad ...(21)$$

$$L_{2} = \frac{imag(Z_{22})}{\omega} = \frac{imag(^{1}/Y_{22})}{\omega} \qquad ...(22)$$

$$L_2 = \frac{imag(Z_{22})}{\omega} = \frac{imag(^1/Y_{22})}{\omega} \qquad ...(22)$$

The EM simulation results are shown in Figure (15) and Figure (16), for the primary and secondary inductors, respectively. The efficiency of the PSCT measured using Equation (6) at 2.45 GHz is 78% as shown in Figure (17). The minimum insertion loss (ILmin) of the transformer is shown in Figure (18), calculated by the following equation [15]:

$$IL_{min}\left(dB\right) = 10\log_{10}\left[1 + \frac{2}{\left(K^{2}Q_{p}Q_{s}\right)} + 2\sqrt{\frac{1}{\left(K^{2}Q_{p}Q_{s}\right)}\left(1 + \frac{1}{\left(K^{2}Q_{p}Q_{s}\right)}\right)}\right] \qquad ...(23)$$

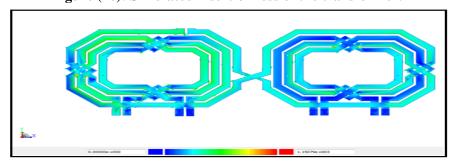

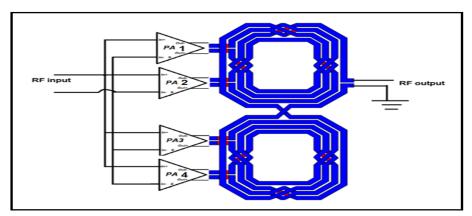

Figure (19) shows the EM simulation of the current density of the transformer, a good distribution of the current is clear, which is a direct thermal effect of the coil. The simplified schematic of the proposed PA based on PSCT is shown in Figure (20).

Figure (14): The Conceptual diagram of the transformer

Figure (15): Simulation results for the primary inductor. (a) Self inductance.

Figure (16): Simulation results for the secondary inductor. (a) Self inductance. (b) Quality factor.

Figure (17): Calculated efficiency of the PSCT.

Figure (18): Simulated insertion loss of the transformer.

Figure (19): Current density simulation of the transformer.

Figure (20):A Simplifies schematic diagram of the designed PA.

Conclusion

A hybrid-type (parallel-series) power-combining transformer was designed to implement a fully-integrated watt level CMOS PA. The designed PA incorporates four stages differential PA based on PSCT. Linear PA class\_AB designed for WLAN applications, it delivers an output power of 30 dBm with PAE of 40% using 2.5 V supply voltage. Nonlinear PA class\_E designed to deliver an output power of 30 dBm with PAE of 54% using 1.6 V supply voltage.

## **REFERENCES**

- [1] J. Kim, W. Kim, H. Jeon, Y. Huang, Y. Yoon, H. Kim, C. Lee and K.T. Kornegay, "A Fully-Integrated High-Power Linear CMOS Power Amplifier With a Parallel-Series Combining Transformer", IEEE Journal of Solid-State Circuits, Vol. 47, No. 3, March, 2012.

- [2] V. Knopik, B. Martineau and D. Belot, "20dBm CMOS Class AB Power Amplifier Design for Low Cost 2GHz-2.45GHz Consumer Applications in a 0.13um Technology", IEEE, 2005.

- [3] M. K. Kazimierczuk," RF Power Amplifiers", John Wiley and Sons, Ltd., Publication, 2008.

- [4] K. J. Kim, T. H. Lim, K.H. Ahn, "The Novel High Efficiency on Chip Transformers for the CMOS Power Amplifier", ISIC 2009.

- [5] J. Javidan, S. M. Atarodi, "Implementation of a Fully Integrated 30-dBm RF CMOS Linear Power Amplifier with Power Combiner", Int. J. Electron. Commun. (AEU) Vol. 65, 2011, PP.502–509.

- [6] A. M. Niknejad, D. Chowdhury, and J. Chen," Design of CMOS Power Amplifiers", IEEE Transactions on Microwave Theory and Techniques, Vol. 60, No. 6, June, 2012, , PP. 1784-1796.

- [7] A. Afsahi and L. E. Larson, "Monolithic Power-Combining Techniques for Watt-Level 2.4-GHz CMOS Power Amplifiers for WLAN Applications", IEEE Transactions on Microwave Theory and Techniques, Vol. 61, No. 3, March, 2013,PP. 1247-1260.

- [8] A. S. Ezzulddin, "Design and Simulation of RF CMOS Power Amplifiers for Portable Systems", Ph.D. Thesis, University of Technology, 2009.

- [9] D. M. Pozar, "Microwave Engineering", John Wiley and Sons Inc., 2<sup>nd</sup> Edition, 1993.

- [10] K. H. An, O. Lee, H. Kim, D. H. Lee, J. Han, K. S. Yang, Y. Kim, J. J. Chang, W. Woo, C. H. Lee, H. Kim and J. Laskar, "Power Combining Transformer Techniques for Fully-Integrated CMOS Power Amplifiers", IEEE Journal of Solid-State Circuits, Vol. 43, No. 5, PP.1064-1075, May, 2008.

- [11] H. Lee, C. Park and S. Hong, "A Quasi-Four-Pair Class-E CMOS RF Power Amplifier With an Integrated Passive Device Transformer", IEEE Transactions on Microwave Theory and Techniques, Vol. 57, No. 4, April, 2009, PP. 752-759.

- [12] Y. Wang and J. Yuan, "An Integrated CMOS High Power Amplifier using Power Combining Technique", IEEE, 2012.

- [13] M. Fathi, D. K. Su and B. A. Wooly, "A 30.3dBm 1.9GHz-Bandwidth 2×4-Array Stacked 5.3GHz CMOS Power Amplifier", IEEE International Solid-State Circuits Conference, 2013.

- [14] D. Tavakolifar, J. Javidan, "Design of Compact Transformer-type Power Combiner for Watt-level PA in CMOS Technology", International Journal of Engineering Research and Applications Vol. 2, Issue 2, 2012, PP 313-321.

- [15] K.T. Ng, B. Rejaei, and J. N. Burghartz, "Substrate Effects in Monolithic RF Transformers on Silicon", IEEE Transactions on Microwave Theory and Techniques, Vol. 50, No. 1, pp. 377-383, January, 2002.