# A 2.4 GHz Differential Class-E Power Amplifier with on-Chip Transformers for Bluetooth Systems

Dr. Abbas H. Issa 🕛

Electrical Engineering Department, University of Technology / Baghdad

Dr. Ahmed S. Ezzulddin

Electrical Engineering Department, University of Technology / Baghdad Sarab M. Ghayyib

Iraq Geological Survey / Baghdad

Email:sarab alani2002@yahoo.com

Received on: 20/8/2013 & Accepted on: 6/3/2014

#### ABSTRACT:

This work presents the design and simulation of a differential class-E Power Amplifier (PA) for class-1 Bluetooth systems in 0.13  $\mu m$  RF CMOS technology. The proposed PA can deliver 21.57 dBm output power to a 50  $\Omega$  load at 2.4 GHz with 65.59 % Power-Added-Efficiency (PAE) from 1 V supply voltage. In order to achieve fully integrated PA, on-chip balun transformers are designed and improved for converting single-ended input signal to differential signal in the input side and differential signal to single-ended output signal in the output side. The results are obtained using microwave office 2009 (version 9.00).

**Keywords:** RF power amplifier, class-E, Bluetooth, CMOS technology, on-Chip balun transformer.

### مضخم قدرة (2.4 GHz) تفاضلي صنف Eمع محولات على الرقاقة لانظمة بلوتوث

### الخلاصة

هذا البحث يقدم التصميم والمحاكاة لمضخم قدرة ( $2.4~\mathrm{GHz}$ ) تفاضلي صنف E لانظمة بلوتوث من الصنف الأول منفذة بتقنية CMOS باجراء ( $0.13~\mu\mathrm{m}$ ). يوفر المضخم المقترح قدرة خرج ( $0.13~\mathrm{CMOS}$ ) وكفاءة قدرة مضافة PAE تساوي ( $0.157~\mathrm{CMOS}$ ) عند تردد( $0.157~\mathrm{CMOS}$ ) بأستخدام مجهز ( $0.157~\mathrm{CMOS}$ ) من تم تصميم وتحسين محولات على الرقاقة وذلك لتحقيق تكامل كلي لتصميم مضخم القدرة المقترح. هذه المحولات تستخدم كوسيلة لتحويل الأشارة احادية النهاية الى اشارة تفاضلية في جهة الادخال والعكس في جهة الاخراج تم الحصول على النتائج باستخدام برنامج المحاكاة (Microwave Office 2009).

### INTRODUCTION

he Bluetooth is recognized as an industry standard for short-range data and voice transfer to link mobile phones, laptops, digital cameras, and other portable devices [1]. It is considered to be a high speed, low cost wireless technology, working with a radio frequency band (called the industrial, scientific, and medical bandor (ISM) for the short) between 2.4-2.48 GHz. This frequency band is free for anyone to use, for any purpose (unlicensed) [2]. For Bluetooth

applications, there are basically three classes based on the transmission distance (100, 10, and 1-meter range), they are Class 1 (The transmitted output power is 20dBm), Class 2 (The transmitted output power is 4dBm) and Class 3 (The transmitted output power is 0dBm), respectively [3].

Today, wireless applications like Bluetooth, WLAN etc. are rapidly growing and there is the need for low cost and high efficiency power amplifier [4]. The design of an on-chip front-end power amplifier with high power efficiency in the mainstream Complementary Metal-Oxide-Semiconductor (CMOS) technology is a challenging problem [5]. The difficulty of CMOS power amplifier lies in the design, including the low breakdown voltage of active devices and low supply voltage. So far, the differential topology has been widely considered as the one of the best solution, and it features a virtual ground, which can cancel the even harmonics. Besides, it will reduce the disturbance to other blocks in the transceiver when it is fully integrated in the system [6].

Since the modulation scheme employed by Bluetooth is Gaussian Frequency Shift Keying (GFSK), which is a constant envelope modulation scheme, a switching-mode (non-linear) PA can be used to achieve high efficiency. Among all classes of nonlinear power amplifiers, the class-E power amplifier is better choice in terms of circuit simplicity and high efficiency and this class has good performance at higher frequency [7].

Murad et al., 2010 [8] presented a 2.4 GHz CMOS single-ended PA for wireless applications in TSMC 0.18 µm CMOS technology. All circuit components, except the output matching network, have been designed on chip. The power amplifier delivered an output power of 19.2 dBm with a PAE of 27.8 % from 3.3 V power supply. Meshkinet al., 2010 [7] designed a switch-mode CMOS class-E power controllable PA suitable for modern wireless communications in TSMC 0.18 µm CMOS process. The designed PA can deliver 21.09 dBm output power to 50  $\Omega$ load at 2.4 GHz with 57 % PAE from 1.8 V supply voltage and the output power can be controlled in 1 dBm steps with small drop in efficiency. Chen et al., 2011 [3] described the design of the two stage of class-E power amplifier for class 1 Bluetooth applications in 0.18 µm CMOS technology with load mismatch protection and power control features. Power control was realized by means of "open loop" techniques to regulate the power supply voltage. Post-layout simulation a 25.1 dBm output power and 54.2 % PAE were achieved at a nominal 1.8 V supply voltage. Raza and Jonas, 2013 [9]presented a novel approach of implementing parallel circuit differential class-E amplifier. A test circuit is implemented in 0.13 µm CMOS process. The power amplifier achieves 22 dBm output power at 2.4 GHz from a 2.5 V with an overall PAE of 38 %.

The outline of this paper is as follows. In section 2, the design of a differential class-E PA for class1 Bluetooth application with two ideal transformers is described. In section 3, the design of on-chip transformers is demonstrated. The simulation results are presented in section 4. Finally, in section 5, conclusions are given.

## DESIGN OF A DIFFERENTIAL CLASS-E PA WITH TWO IDEAL TRANSFORMERS

The design starts with the single-ended class-E PA followed by the differential configuration with two ideal transformers as following:

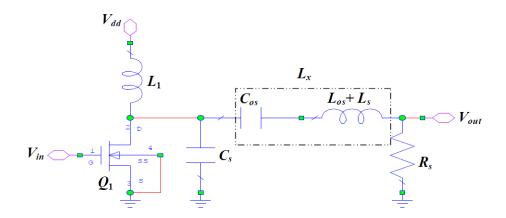

The circuit topology (basic circuit) of a class-E power amplifier is shown in Figure (1) [10]. In this circuit  $L_1$  represents the drain bias RF choke,  $V_{dd}$  is the drain supply voltage,  $C_s$  is the capacitor shunting the active device  $(Q_1)$ ,  $L_s$  is the class

inductance,  $L_{os}$  and  $C_{os}$  constitute a series resonant circuit tuned at the operating frequency,  $L_x$  is the excess (resultant) inductance and  $R_s$  is the optimum resistance seen by the load network for the required output power. The active device,  $Q_1$ , (MOSFET in this case) operates as an ON/OFF switch.

Figure (1): Typical class-E power amplifier with shunt capacitance configuration.

The component values of the circuit in Figure 1 are calculated at output power  $P_{out} = 50$  mw (17 dBm), operating frequency  $f_o = 2.4$  GHz, loaded quality factor $Q_{Ls} = 10$  and drain supply voltage = 1 V using the following equations [10]:

$$C_s = \frac{P_{out}}{\pi * \omega_o * V_{dd}^2} \qquad \dots (1)$$

$$R_{s (opt)} = 0.577 \left(\frac{V_{dd}^2}{P_{out}}\right)$$

...(2)

$$R_{s (opt)} = 0.577 \left(\frac{V_{dd}^2}{P_{out}}\right) \qquad ...(2)$$

$$L_x = \frac{\pi * V_{dd}^2 (\pi^2 - 4)}{2 * \omega_o * P_{out} (\pi^2 + 4)} \qquad ...(3)$$

where  $\omega_o = 2\pi f_o$ .

The value of  $L_1$  can be calculated by the resonant equation of an LC tank as follow:

$$L_1 = \frac{1}{\omega_0^2 c_1} = \frac{1}{\omega_0^2 (c_p - c_s)} \qquad \dots (4)$$

$C_1$ : the cancelation capacitance by the inductor,

$C_p$ : exact shunt capacitance at the drain of the transistor, and

$C_s$ : capacitance of the class.

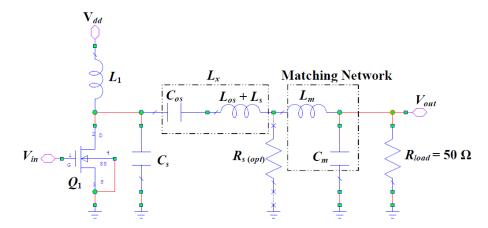

In order to match a 50  $\Omega$  load, an up-conversion matching network is implemented to transform an optimum load to a 50  $\Omega$  load. L-matching network is chosen because of its circuit simplicity. Also, the excess inductance  $(L_{\varphi})$  in a class-E power amplifier can be combined with the inductor used in the matching network if a low-pass L matching network is used. Therefore, the schematic of a class-E power amplifier is modified as shown in Figure (2).

The values of  $L_m$ ,  $C_m$  and  $L_{total}$  can be calculated using the following equations [11]:

$$L_m = \frac{\sqrt{R_{opt}(R_L - R_{opt})}}{\omega_o} \qquad ...(5)$$

$$C_m = \frac{\sqrt{\frac{(R_L - R_{opt})/R_{opt}}{R_D}}}{\omega_o} \qquad \dots (6)$$

$$L_{total} = L_x + L_m \qquad ...(7)$$

Using Equation (1) to Equation (7), the calculated component values for single-ended class-E power amplifier are summarized in Table (1).

Figure (2): Complete schematic (single-ended) of a class-E power amplifier.

Table (1): Component values of the single-ended class-E PA.

| Component    | Value | Unit |

|--------------|-------|------|

| $C_s$        | 0.73  | pF   |

| $R_{s(opt)}$ | 16.60 | Ω    |

| $L_1$        | 2.00  | nН   |

| $L_x$        | 1.26  | nН   |

| $L_m$        | 1.56  | nН   |

| $C_m$        | 1.87  | pF   |

| $L_{total}$  | 2.83  | nН   |

The final step in the design is combining of two single-ended topology to produce differential topology and then using two ideal transformers, the first one in the input side is to convert single ended input signal to differential signal and the second in the output side is to convert the differential signal to single-ended 50  $\Omega$  load signal as shown in Figure (3). The additional objective of using ideal transformers is obtaining the primary results.

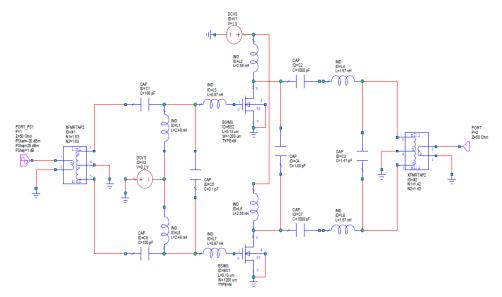

Figure (3): The proposed differential class-E power amplifier with two ideal transformers.

### DESIGN OF ON-CHIP TRANSFORMERS

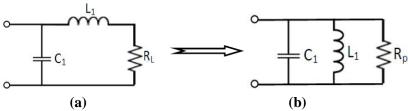

On-chip transformers contribute substantially in enhancing reliability, efficiency, and performance of silicon-integrated Radio-Frequency (RF) circuits. Many researchers have reported the integration of on-chip transformers in PAs [12]. In order to design on-chip transformers instead of the ideal transformers, which used with the proposed class-E PA of Figure 3, the inductance required for each winding of the transformer must be determined from consideration of the terminal impedances and center frequency specification. As a first step, L-section matching network that employed in the proposed design is converted to parallel section matching network as shown in Figure 4. In these networks  $L_1$  represents the inductance of the primary winding,  $R_p$  is the parallel (differential) resistance,  $R_L$  is the output resistance, which is typically 50  $\Omega$ ,  $R_{opt}$  is the optimum resistance seen by the load network of the class-E PA and  $C_1$  locates in parallel to the inductance.

Figure (4): Matching networks, (a) L-section, (b) parallel section.

This conversion process is achieved using the following equations [13]:

$$R_p = R_{(differential)}$$

...(8)

$R_{(differential)} = 2R_{(opt)}$  ...(9)

$$R_p = \frac{L_1^2 \omega_0^2}{R_L} \qquad ...(10)$$

$$R_{(differential)} = 2R_{(opt)}$$

$$R_{p} = \frac{L_{1}^{2}\omega_{o}^{2}}{R_{L}}$$

$$C_{1} = \frac{1}{L_{1}\omega_{o}^{2}}$$

...(10)

According to the on-chip (1:1) square transformer, the value of the inductance for secondary winding can be calculated from:

$$n = \left(\frac{L_2}{L_1}\right)^{\frac{1}{2}}$$

...(12)

In the proposed PA, the component values of the parallel matching network are calculated using Equation (8) to Equation (12), at load resistance  $R_L = 50 \Omega$ , operating frequency  $f_o = 2.4$  GHz, turn ratio n = 1, and the optimum resistance  $R_{opt}$ = 16.6  $\Omega$ . The calculated values are summarized in Table (2).

Table (2): Component values of the Parallel matching network.

| Component | Value | Unit |

|-----------|-------|------|

| $L_1$     | 2.7   | nН   |

| $L_2$     | 2.7   | nН   |

| $C_1$     | 1.62  | pF   |

The design of an on-chip transformer is dependent on the available process. Nonetheless, good efficiency of the transformer can be obtained by increasing the magnetic coupling factor (k) and improving the quality factor (Q) of the coupled inductors, that is; minimizing of the minimum insertion losses ( $IL_{min}$ ). In order to improve coupling factor, the wide metal traces of the transformer can be split into multiple parallel segments and interleaved [14].

In the next step of the design, the dimensions of the transformer (outer dimension  $(D_{out})$ , width of primary and secondary traces  $(W_p, W_s)$ ) are adjusted until the inductances for primary and secondary winding approaching to the values which calculated from matching network in Table (2). Virtually, for 1:1 square transformer with geometrical parameters that are illustrated in Table (3), the onchip balun transformer (a device which converts a single ended (unbalanced) signal to a differential (balanced) signal and vice versa) is designed and optimized using the following design equations [14]:

$$Q_p = \frac{Im(Z_{11})}{Re(Z_{11})}$$

and  $Q_s = \frac{Im(Z_{22})}{Re(Z_{22})}$  ...(13)

$$k = \sqrt{\frac{Im(Z_{12}) \cdot Im(Z_{21})}{Im(Z_{11}) \cdot Im(Z_{22})}} \dots (14)$$

$$Q_{p} = \frac{Im(Z_{11})}{Re(Z_{11})} \quad \text{and} \quad Q_{s} = \frac{Im(Z_{22})}{Re(Z_{22})} \qquad ...(13)$$

$$k = \sqrt{\frac{Im(Z_{12}) \cdot Im(Z_{21})}{Im(Z_{11}) \cdot Im(Z_{22})}} \qquad ...(14)$$

$$IL_{min}(dB) = 10\log_{10} \left[ 1 + \frac{2}{(K^{2}Q_{p}Q_{s})} + 2\sqrt{\frac{1}{(K^{2}Q_{p}Q_{s})}} \left( 1 + \frac{1}{(K^{2}Q_{p}Q_{s})} \right) \right] ...(15)$$

The primary and the secondary inductances can be calculated in terms of  $R_1$  and  $R_2$ ,  $Q_1$  and  $Q_2$  for primary and secondary respectively, i.e.

$$L_1 = \frac{Q_1 R_1}{\omega_0}$$

and  $L_2 = \frac{Q_2 R_2}{\omega_0}$  ...(16)

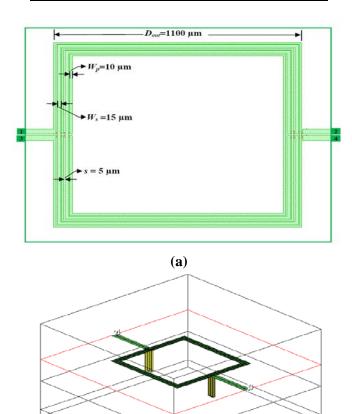

In this design, a standard 0.13 µm CMOS process with two aluminum metal layers is used. This process provides the top metal of 3 µm thickness and the dielectric thickness of 4 µm. Figure 5 shows the Electro-Magnetic Sight (EMSight) setup for on-chip balun transformer.

Table (3): Geometrical parameters and simulation results for on-chipbalun transformer.

| Geometrical parameters |      | Simulation results      |      |  |

|------------------------|------|-------------------------|------|--|

| $D_{out}(\mu m)$       | 1100 | $L_{p}\left( nH\right)$ | 2.9  |  |

| $W_p(\mu \mathbf{m})$  | 10   | $L_s(\mathbf{nH})$      | 3.3  |  |

| $N_{seg}$              | 3    | $Q_p$                   | 11.6 |  |

| $W_s(\mu m)$           | 15   | $Q_s$                   | 11.9 |  |

| $N_{seg}$              | 2    | K                       | 0.7  |  |

| s(µm)                  | 5    | $IL_{min}(dB)$          | 1.2  |  |

Figure (5): EMSight setup for on-chip (1:1) balun transformer, (a) Top view, and (b) Orthogonal view.

**(b)**

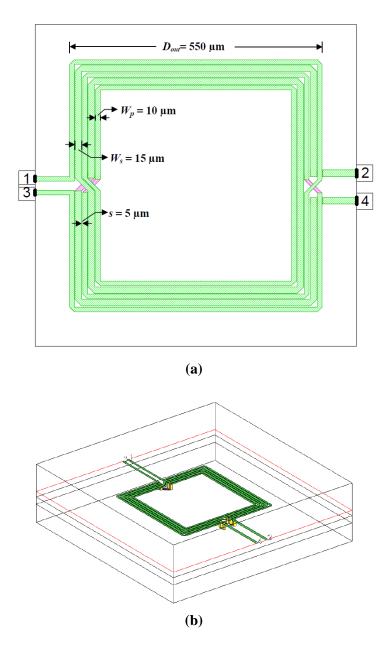

To reduce the size of the on-chip balun transformer (area-efficient), the primary and secondary coils of this transformer are turned into two windings instead of one winding.

In addition, to minimize the losses (heat) that is generated due to the orthogonal edge at each corner of the primary and secondary traces of the transformer; the orthogonal edge is converted to lapped edge. Figure 6 shows the on-chip balun transformer design after improvement.

Figure (6): EMSight setup for on-chip (1:1) improvement balun transformer (a) Top view, and (b) Orthogonal view.

### SIMULATION RESULTS

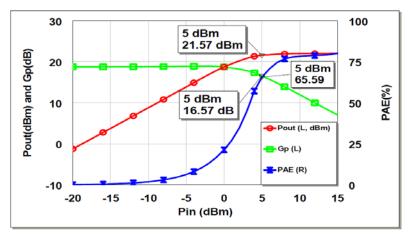

The proposed power amplifier is designed and simulated using microwave office 2009(version 9.00) [15], with all the devices optimized to achieve the required Bluetooth performance. Figure (7) shows the simulated output power,

power gain, and power-added-efficiency versus input power at a frequency of 2.4 GHz. The PA provides 21.57 dBm of output power with a maximum gain of 16.57 dB and a PAE of 65.59% for an input power of 5 dBm as shown in Figure (7)

Figure (7): Output power (Pout), power gain (Gp), and power-added-efficiency (PAE) versus input power (Pin) at a frequency of 2.4 GHz for the proposed PA.

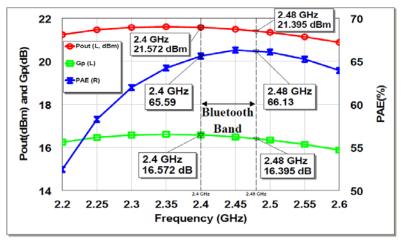

The simulated performance of the PA as a function of frequency for an input power of 5 dBm is presented in Figure (8). As shown from this figure, the gain of the prototype PA remains almost flat over the class-1 Bluetooth band, which is from 2.4 GHz to 2.48 GHz. The minimum PAE is 65.59% while the output power is above 21.39 dBm for the entire class-1 Bluetooth band, thereby, fulfilling the 20-dBm output power requirement.

Figure (8): Output power  $(P_{out})$ , power gain  $(G_P)$ , and power-added-efficiency (PAE) versus frequency for  $P_{in}$  of 5 dBm, for the proposedPA.

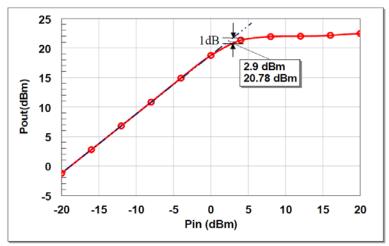

In order to estimate the linearity of the proposed PA, the compression characteristics are plotted in Figure (9). As shown from this figure, the power amplifier reaches its output 1dB compression at 20.78 dBm, with an input power level of 2.9 dBm. The BSIM3v3.3 model [16] for MOSFET transistor is used in the power amplifier simulation.

Figure (9): Compression characteristic (1-dB compression point) at a frequency of 2.4 GHz.

Finally, to verify the feasibility of the segmentation idea in the balun transformer performance improvement, a square transformer with segmentations is simulated using EMSight simulator. EMSight simulator is an electro-magnetic solver provided with Microwave Office (MWO) 2009 RF/Microwave software tools. The geometrical parameters for balun transformer and the simulation results are summarized, previously, AS in Table (3).

Table (4) shows the geometrical parameters and the simulation results for the improvement balun transformer. A comparison between the results in Table (3) and Table (4) show that the values of  $L_p$ ,  $L_s$ ,  $Q_p$ ,  $Q_s$ , k, and  $IL_{min}$  are remained approximately the same, with reduction in the area required for implementing the transformer.

Table (4): Geometrical parameters and simulation results for on-chip improvement balun transformer.

| Geometrical par       | Simulation results |                        |      |

|-----------------------|--------------------|------------------------|------|

| $D_{out}(\mu { m m})$ | 550                | $L_p(\mathbf{nH})$     | 2.8  |

| $W_p$ ( $\mu$ m)      | 10                 | $L_s(nH)$              | 3.31 |

| $N_{seg}$             | 3                  | $Q_p$                  | 11.7 |

| $W_s$ ( $\mu$ m)      | 15                 | $Q_s$                  | 12   |

| $N_{seg}$             | 2                  | k                      | 0.68 |

| s (µm)                | 5                  | IL <sub>min</sub> (dB) | 1.22 |

### **CONCLUSIONS:**

The design and simulation of a power amplifier for class-1 Bluetooth system in 0.13  $\mu m$  CMOS technology is presented. By using differential topology with two ideal transformers,  $P_{\text{oldB}}$  of 20.78 dBm can be achieved at 2.9 dBm input power. The proposed power amplifier can deliver 21.57 dBm output power to a 50  $\Omega$  load at 2.4 GHz with 65.59 % power-added-efficiency (PAE) and 16.57 dB from 1V

supply. The designed on-chip balun transformer used in this work plays two roles: First, it is used to transform the 50  $\Omega$  load. Second, it converts a differential signal into single-ended signal so that it can be connected to the antenna directly, and it converts a single-ended signal to differential signal in the input side.

The characteristics of the PA, accompanied by those of the other Bluetooth PAs, are summarized in Table 5. As a comparison with other listed CMOS PAs for Bluetooth applications, this amplifier has the highest power-added-efficiency, lowest supply voltage, good output power, medial linearity, and no external components are required.

Finally, all the results are obtained from the simulation, and there is the need for fabricating this proposed design to verify the results, practically, presented in this work.

| Reference     | Year | CMOS    | $P_{out}(\mathrm{dBm})$ | Gp(dB) | PAE (%) | $V_{pa}(V)$ | Class | <b>External</b> component |

|---------------|------|---------|-------------------------|--------|---------|-------------|-------|---------------------------|

| [15]          | 2010 | 0.18µm  | 19.2                    | 15     | 27.8    | 3.3         | E     | Yes                       |

| [07]          | 2010 | 0.18µm  | 21.09                   | 16.09  | 57      | 1.8         | E     | Yes                       |

| [03]          | 2011 | 0.18µm  | 25.1                    | 20.1   | 54.2    | 1.8         | E     | No                        |

| [16]          | 2013 | 0.13 μm | 22                      | •      | 38      | 2.5         | E     | No                        |

| This<br>work* | 2013 | 0.13 μm | 21.57                   | 16.57  | 65.59   | 1.0         | E     | No                        |

Table (5): Comparison with other Bluetooth PAs.

### REFERENCES

- [1] Li,L., Huang,Jiao,Y., ZhengX., and Wang, S., "Low power RF transceiver design for Bluetooth applications," IEEE International Conference on Solid-State and Integrated-Circuit Technology, pp. 1552-1555, 2008.

- [2] Miller, M., Discovering Bluetooth, USA: SYBEX, 2001.

- [3] Chen, W., Lin, W., and Huang, Sh., "A novel VSWR protected and controllable CMOS class E power amplifier for Bluetooth applications," International Journal of Design, Analysis and Tools for Circuits and Systems, Vol. 1, No. 1, pp. 22-26, June, 2011.

- [4] Vasylyev, A., Weger, P., Bakalski, W., Thuringer, R.,and W. Simburger, W., "A monolithic 2.4 GHz, 0.13 μm CMOS power amplifier with 28 dBm output power and 48% PAE at 1.2 V supply," International Crimean Conference on Microwave and Telecommunication Technology, pp. 98-99, 2004.

- [5] Datta, S., and Saha, H., "A 950-MHz fully differential class-E power

<sup>\*</sup>Simulation

- amplifier in 0.18µm CMOS for wireless communications," International Conference on Emerging Trends in Electronic and Photonic Devices and Systems, pp. 88-91, 2009.

- [6] Jin, B., Wu, Q., Yang, G., Meng, F., Fu, J., and Tang, K., "Fully-integrated CMOS power amplifier design for WiMAX application with semi-lumped transformer," IEEE International Conference on Industrial Informatics, pp. 181-185, July, 2008.

- [7] Meshkin, R., Saberkari, A., and Niaboli-Guilani, M., "A Nnovel 2.4 GHz CMOS class-E power amplifier with efficient power control for wireless communications," IEEE International Conference on Electronics, Circuits and Systems, pp. 599-602, 2010.

- [8] Murad, S.A.Z., Pokharel, R.K., Kanaya, H., and Yoshida, K., "A 2.4 GHz 0.18-μm CMOS class E single-ended power amplifier without spiral inductors," IEEE Journal of Solid-State Circuits, pp. 25-28, 2010.

- [9] Raza, K. H., Jonas, F., Atila, A. and Qamar, W., "A parallel circuit differential class-E power amplifier using series capacitance," Journal of Analog Integrated Circuits and Signal Processing, Vol. 75, pp. 31-40, 2013.

- [10] Sokal, N., and Sokal, A., "Class E a new class of high-efficiency tuned single-ended switching power amplifiers," IEEE J. Solid-State Circuits, Vol. SC-10, pp. 168–176, June, 1975.

- [11] Pozar, D. M., Microwave Engineering" John Wiley and Sons Inc., 2<sup>nd</sup> edition, 1993.

- [12] El-Gharniti,O., Kerherve,E., and Begueret, J.-B, "Modeling and characterization of on-chip transformers for silicon RFIC," IEEE Transactions on Microwave Theory and Techniques, Vol. 55, No. 4, pp. 607-615, April, 2007.

- [13] Razavi, B.,RF Microelectronics, Pearson Education Inc., 2<sup>nd</sup> edition, 2012.

- [14] Ezzulddin, A. S., Ali, M. H.,and Abdulwahab, M. Sh., "On-chip RF transformer performance improvement technique," Engineering and Technology Journal, Vol. 28, No. 4, pp. 676-685, 2010.

- [15] Applied Wave Research Web Site [Online]. Available: http://www.appwave.com

- [16] BSIM Web Site [Online]. Available:http://wwwdevice.eecs.berkeley.edu/~bsim3/bsim4\_get.htl