# Electrical Characteristics of Silicon p-n Junction Solar Cells Produced by Plasma-Assisted Matrix Etching Technique

Oday A. Hamadi<sup>\*</sup>

Ban A.M. Bader \*\*

Afnan K. Yousif \*\*

Received on: 20/2/2007 Accepted on: 3/1/2008

#### **Abstract**

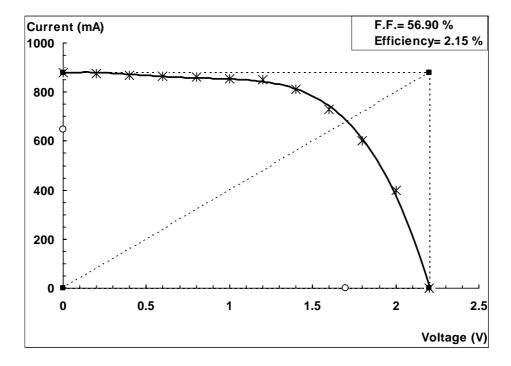

In this work, plasma-induced matrix etching technique was used to fabricate p-n junction solar cells and their electrical characteristics were studied. Results showed reasonable improvement in solar cell characteristics when compared to the characteristics of the cells fabricated without etching process or by conventional thermal evaporation technique. The maximum conversion efficiency of the fabricated cells was about (2.15%) at irradiation power of (90W/cm²) and the fill factor was (56.90%).

(2.15%)

.(56.90%)

$(90 \text{W/cm}^2)$

#### 1. Introduction

Crystalline silicon solar cells are nowadays well performing and reliable, commercially available and widely used in a variety photovoltaic systems. However, their cost is still too high to be competitive with classical electricity production. Therefore, photovoltaic devices are mainly used in nice markets. It will not be possible that a substantial part (e.g. a few percent) of the electricity be produced by photovoltaic systems, until the cell and panel cost is reduced with a factor of about five. There is doubt that a larger production volume and normal technological evolution eventually enable such a drastic cost reduction. The physical reason for the shortcomings of silicon as a solar cell material is its poor optical absorption coefficient  $\alpha(\lambda)$ . If no technological

sophistication for enhanced light trapping is introduced, a silicon wafer of 200µm thickness is needed to absorb the sunlight almost completely. As a consequence, a minority carrier diffusion length larger than 100µm is needed to collect the generated electrons and holes. The need for thick cells of high crystalline quality is inherent to silicon, and this is the main reason for the high cell cost [1]. In thin film solar cells the physical and chemical properties of the interfaces between the different layers mainly determine the electronic device properties [2].

The fact that a gas discharge containing charged (ion) and neutral (radical) species can be used to initiate chemical processes required for etching of a substrate placed inside [3]. All etching techniques

include the removal of a layer from the sample surface in a specified crystalline direction (orientation) and due to the chemical reaction between sample surface and the particles performing etching process. The nature of chemical reaction determines the crystalline orientation in which the particles are removed. Hence. the major parameters affecting this reaction, such temperature and pressure, can be considered as controllers to the characteristics of the etched surfaces.

High charge density plasmas are being used increasingly in etching silicon and other semiconductors. Such etching reactors use one of several types of high-charge density sources, such as helical resonators (HR), electron cyclotron resonance (ECR) plasmas and inductively coupled plasmas (ICP). These sources share defining characteristics independent control of the ion strikes the wafer. Consequently, in some ways, thin film processes induced by these different sources are thought to be interchangeable. However, the mechanism of plasma-induced etching may be different for these sources [4].

Plasma-induced etching processes have found an increasingly important role as the interest in micro-fabrication continues to grow. Plasma-induced etching processes utilize the thermal action to locally accelerate chemical etching reaction on the surface of a solid, which is preferred sometimes situated in a suitable liquid or gas etchant [5]. In gaseous or liquid reactive environments, the material removal effected by localized activation of chemical reactions at much lower surface temperatures than ablation techniques. The plasmainduced etching technique is one of the non-contact, flexible and accurate processes applicable to a wide range

of materials. The technique can offer advantages over conventional techniques in terms of process simplicity, flexibility and cost efficiency [6].

Plasma-induced etching processes have been investigated for a wide variety of applications in the field of micro-fabrication by many works [3, 7-11]. achievements include a wide variety of driven processes that can be used to directly and controllably etch fine features in solid materials. A number of studies have shown that plasma-induced or plasma-assisted chemical etching can be applied to numerous materials such as metals. ceramics, semiconductors. some polymers [12-13].

### 2. Experimental Work

The samples used in this work were n-type silicon substrates of resistivity,  $2x2cm^2$  $(3\Box.cm)$ dimensions and 500 m thickness. These samples were washed with distilled water then rinsed in ethanol and subjected to the ultrasonic waves for 10 minutes, then dried by hot air. The samples were grinded and polished until a mirror-like surface was resulted. Then they were cleaned with CP-4 (HNO<sub>3</sub>: HF: CH3CooH) (1:3:3) solution for 5 minutes to remove any residual oxides might be induced on the surface due to friction. After with, these samples were rinsed in ethanol to remove acids then dried to be ready for processing.

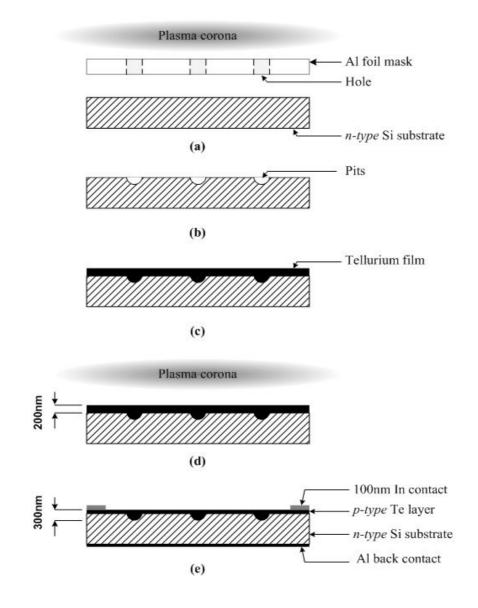

plasma-induced The etching system was initially evacuated at 10<sup>-8</sup> mbar (diffusion pumps) to remove any residuals inside the chamber but it was then operated at 10<sup>-6</sup> mbar. The anode of electric discharge system is made of stainless steel and the silicon substrate to be etched is mounted on the cathode at a specified opposite distance from the anode. discharge maximum voltage 15kV<sub>DC</sub> and the discharge current reaches to 3A. Argon gas of 1mbar pressure was employed to generate the discharge plasma. In order to make a matrix of pits on the substrate surface, a 0.5mm thickness mask (as shown schematically in Fig.1) made of aluminium foil was placed on the substrate surface in front of plasma corona. The sample was placed inside the processing chamber for 5 minutes before being removed and tested.

200nm (crystal thickness moniter) thin films of p-type tellurium were deposited on the processed substrates the same plasma-assisted by deposition system. This process includes both depositing and heattreating processes. Indium layer of 200nm thickness was deposited on the surface to represent electrode. Another group of solar cells were fabricated without etching step to introduce the effect of this process on the characteristics of the produced cell. The experimental steps of this work are explained in Fig.2. Electrical measurements include I-V and C-V for the p-n junction, shortcircuit current, open-circuit voltage. conversion and fill factor for the fabricated solar cell. A Farnell DC power supply, Keithly-616 digital multimeter and hp/4192 ALF C-V device were used to perform electrical measurements. A 120W maximum power halogen lamp of adjustable intensity (0-230) W/cm<sup>2</sup> for irradiation was used measurements. In order to measure the maximum conversion efficiency, several load resistors  $(1 \square - 5k \square)$  were connected to the device during characterization.

### 3. Results and Discussion

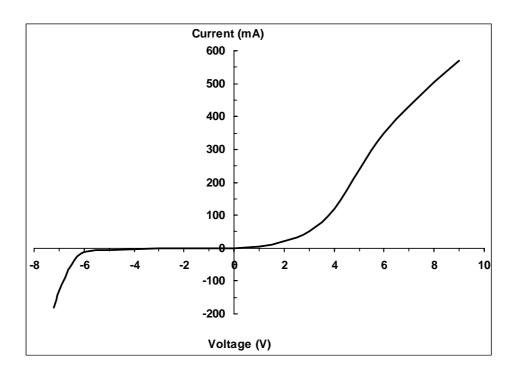

Figure (3) shows the I-V characteristics in dark for the fabricated p-n junction. The behavior of the curve is typical for most junctions and the forward current reaches its maximum at about 520mA at 9V bias voltage. In the reverse

bias, the current does not exceed 10mA until the device reaches breakdown at 7V.

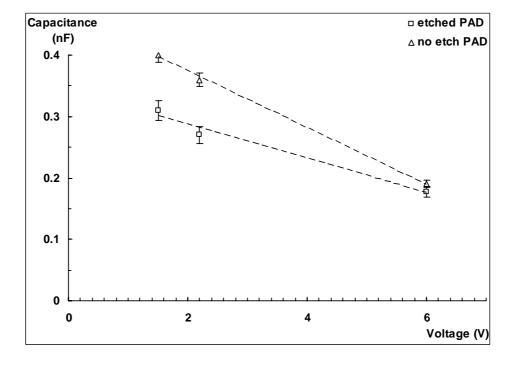

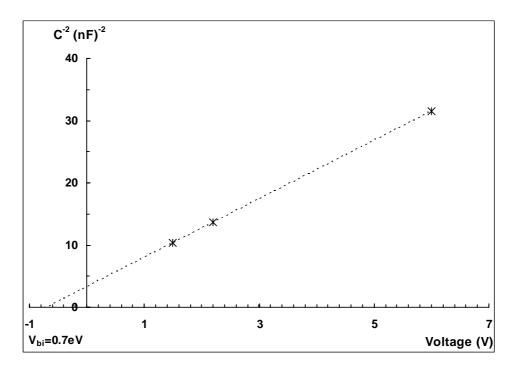

The relation between capacitance (C) and voltage in reverse condition was plotted in Figure (4). There was reasonable reduction in junction capacitance due to substrate etching and this effect may be interpreted as follows. The formation of regions (pits) will increase the carrier transfer from both sides of junction. As the substrate is n-type, i.e., the majority carriers (electrons) will transfer toward the junction region to recombine with the majority carriers in the p-type side (holes). This will decrease the carrier concentration at the junction edges and the built-in potential will consequently increase, which causes the capacitance inside the depletion layer to decrease.

The effect of etching process may be interpreted as follows. Formation of pits on the substrate surface and consecutive heat-treating allow the Te layer to form deep junction inside the n-type silicon substrate with radial distribution and less energy requirement. Hence, the low-energy incident photons will be collected by the reflections occurring inside the pit in addition to the original absorption process in the p-type layer. As well, the low-energy incident photons may escape along the plane parallel to the iunction region without Such photons absorbed. will definitely been "trapped" by these electrically effective and optically high-density regions pits due to optical coupling and dynamic effects. This effect may be little similar to that of quantum wells but with no changes in structure. Formation of 16 pits, each of 1mm diameter and 200nm depth, may increase the volume of the p-n junction region by about 1.3%. Controlling plasmaprocessing parameters may make it possible to achieve required Electrical Characteristics of Silicon p-n Junction Solar Cells Produced by Plasma-Assisted Matrix Etching Technique

increasing in the volume of the upper formed layer and hence the p-n junction. Also, formation of too many smaller pits may improve the results much more due to increasing the absorption of the low-energy incident photons in the p-type layer and allow the higher-energy photons to pass toward the junction region.

#### 4. Conclusions

According to the obtained results in this work, a p-n junction was plasma-assisted formed using deposition technique including plasma-induced etching of silicon substrate. A p-n junction solar cell was fabricated and characterized at AM1.5 irradiation condition. Measurements showed that the fabricated solar cell is higher in conversion efficiency (2.15%) and fill factor (56.90%) when compared to the devices fabricated without etching process. As etching process is simple and low cost, mass production of such devices may employ effectively.

## References

- [1] M. Burgelman, Thin Film Solar Cells By Screen Printing Technology, Proceeding of the Workshop Microtechnology and Thermal Problems in Electronics, Technical University of Lodz, 1998, pp.129-135.

- [2] J. Fritsche, T. Schulmeyer, A. Thißen, A. Klein and W. Jaegermann, *Thin Solid Films*, 431-432, 267–271 (2003).

- [3] D.M. Manos and D.L. Flamm, Plasma Etching: an

**Introduction** (Academic Press, Inc. San Diego, 1989).

- [4] J.W.A.M. Gielen, W.M.M. Kessels, M.C.M. van de Sanden and D.C. Schram, *J. Appl. Phys.* **82**, 2643 (1997).

- [5] D.J. Ehrlich, J.Y. Tsao (eds.): Laser Microfabrication-Thin film Processes and Lithography (Academic Press, Inc. New York, 1989).

- [6] R.J. von Gutfeld and R.T. Hodgson, *Appl. Phys. Lett.* **40**, 352 (1982).

- [7] P.A. Moskowitz, D.R. Vigliotti, and R.J. von Gutfeld, *Polyimides* **1**, 365 (1984).

- [8] M. Datta, L.T. Romankiw, D.R. Vigliotti, and R.J. von Gutfeld, *Appl. Phys. Lett.* **51**, 2040 (1987).

- [9] R.J. von Gutfeld, D.R. Vigliotti, and M. Datta, J. Appl. Phys. 64, 5197 (1988).

- [10] W. Hussey, B. Haba, and A. Gupta, *Appl. Phys. Lett.* **58**, 2851 (1991).

- [11] R. Nowak, S. Metev, and G. Sepold, *Mater. & Manuf. Proc.* **9**, 429 (1994).

- [12] J. Y. Cheo and I.P. Herman, *J. Vac. Sci. Technol. A* **15**, 3024 (1997).

- [13] V.M. Donnelly, M.V. Malyshev, M. Schabel, W. Tai, .P. Herman and N.C. Fuller, *Plasma Sources Sci. Technol.* 11, A26 (2002).

Figure (1) The explanation of the matrix-punctuated mask used in this work

Figure (2) Experimental steps of this work

(a) and (b) processing with plasma and formation of pits, (c) depositing of Te thin film,

(d) plasma-treating and (e) the structure of the fabricated p-n junction solar cell

Figure (3) The I-V characteristics in dark of the p-n junction at 750W processing power

Figure (4) The C-V relation of the p-n junction for both cases: etched and not etched substrate

Figure (5) The C<sup>-2</sup>-V relation of the p-n junction in reverse bias.  $V_{bi}$ =0.7eV

Figure (7) The I-V characteristics of the fabricated solar cell under AM1.5 illumination. The maximum current ( $I_m$ ) is 880mA, maximum voltage ( $V_m$ ) is 2.2V, short-circuit current ( $I_{SC}$ ) is 648mA and open-circuit voltage ( $V_{OC}$ ) is 1.7V, then the fill factor is 56.90%.